芯片級靜電放電(ESD)保護電路設計 硬件防護與軟件開發協同

在集成電路(IC)設計與制造中,靜電放電(ESD)保護電路的設計至關重要。它直接關系到芯片在制造、封裝、測試及最終應用中的可靠性與良率。一個完整的ESD防護體系不僅涉及精密的硬件電路設計,也離不開配套的軟件開發與驗證工具的支持。本文將探討MOS芯片ESD保護電路的設計要點,并闡述軟件開發在此過程中的協同作用。

一、ESD保護電路的核心設計原理

ESD保護電路的核心任務,是在芯片引腳與內部核心電路之間構建一個可控的低阻抗放電路徑,在極短時間內(納秒級)泄放高達數千伏的ESD脈沖,并將內部電路兩端的電壓鉗位在安全水平。對于基于MOS工藝的芯片,設計需重點關注:

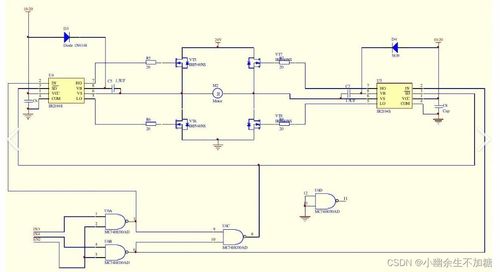

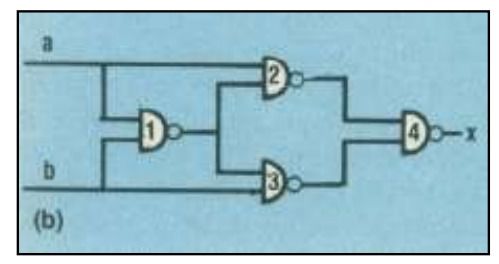

- 觸發機制:設計能快速響應ESD事件的觸發電路,如RC觸發的MOS管、柵極接地NMOS(GGNMOS)或硅控整流器(SCR)。

- 泄放能力:確保保護器件具有足夠的尺寸和結構,以承載大電流而不失效。這需要精確的布局布線(Layout),避免電流集中和熱失效。

- 布局與寄生效應:保護器件必須緊鄰焊盤放置,以最小化寄生電阻和電感。需仔細評估保護電路本身引入的寄生電容對高速信號完整性的影響。

- 全芯片防護網絡:建立從所有輸入/輸出(I/O)引腳、電源軌到地的完整協同防護網絡,確保ESD電流有預設的全局泄放路徑。

二、ESD保護的硬件設計流程與方法

典型的設計流程包括:

- 標準與目標設定:依據JEDEC、AEC-Q100等行業標準(如人體模型HBM、機器模型MM、充電器件模型CDM)設定防護等級。

- 器件選型與仿真:利用TCAD(工藝計算機輔助設計)工具仿真保護器件在ESD應力下的電熱行為。使用SPICE模型進行電路級仿真,驗證觸發電壓、維持電壓和鉗位特性。

- 版圖實現:采用多指狀(multi-finger)結構、增加接觸孔、使用啞元(dummy)器件等版圖技巧來提升均勻性和魯棒性。電源鉗位(Power Clamp)電路的設計與分布也是關鍵。

- 測試驗證:通過片上測試結構和專門的ESD測試儀進行硅后驗證,確保設計達標。

三、軟件開發在ESD設計中的關鍵作用

軟件開發并非直接設計保護電路,而是通過提供自動化工具、模型和流程,極大地提升設計效率和準確性:

- 設計與仿真自動化:

- EDA腳本與平臺:使用Perl、Python或Tcl腳本自動生成保護單元的版圖,或集成不同仿真工具的工作流。

- 模型開發:開發精確的ESD器件緊湊模型(Compact Model),供電路仿真器使用。這需要軟件工程師與器件物理專家緊密合作。

- 驗證與檢查:

- 電氣規則檢查(ERC):開發定制化的ERC規則,用于檢查版圖中ESD路徑的連通性、是否存在懸空柵極等。

- 布局與原理圖對比(LVS):確保復雜的ESD保護網絡版圖與電路圖完全一致。

- 寄生參數提取:提取保護網絡及互連線的寄生電阻/電容/電感,進行更精確的仿真。

- 數據分析與良率管理:

- 測試數據分析軟件:開發或使用軟件分析大量ESD測試數據,快速定位失效點和薄弱環節,進行統計良率分析。

- 知識庫與IP管理:建立可重用的ESD保護電路知識產權(IP)庫,并通過軟件進行版本管理和集成驗證。

四、硬件與軟件的協同優化

最先進的ESD設計是硬件與軟件深度協同的結果。例如,利用機器學習的軟件算法,可以分析歷史測試數據和仿真結果,預測新設計的最佳保護器件尺寸和布局參數,從而減少設計迭代次數。針對特定應用(如超高頻RF芯片),需要通過軟件協同仿真,精細權衡ESD防護等級與信號性能(如插入損耗)。

結論

MOS芯片的ESD保護電路設計是一個多學科交叉的工程領域。強大的硬件設計是確保芯片物理堅固性的基石,而高效的軟件開發則是實現設計自動化、驗證嚴謹化和分析智能化的翅膀。二者相輔相成,共同構成了現代高可靠性芯片設計中不可或缺的防護體系。隨著工藝節點不斷演進和芯片復雜度提升,這種“硬軟結合”的協同設計方法將變得愈加重要。

如若轉載,請注明出處:http://www.ruling123.cn/product/84.html

更新時間:2026-04-12 20:04:11